Báo cáo học liệu

Mua học liệu

Mua học liệu:

-

Số dư ví của bạn: 0 coin - 0 Xu

-

Nếu mua học liệu này bạn sẽ bị trừ: 2 coin\Xu

Để nhận Coin\Xu, bạn có thể:

Bài 22. Một số mạch xử lí tín hiệu trong điện tử số SVIP

I. MẠCH LOGIC TỔ HỢP

1. Khái niệm mạch logic tổ hợp

- Mạch logic tổ hợp là loại mạch được cấu tạo từ các cổng logic cơ bản.

- Đầu ra của mạch tại một thời điểm cụ thể:

+ Dựa vào sự kết hợp các trạng thái của lối vào tại thời điểm đó.

+ Không bị ảnh hưởng bởi các giá trị lối ra trước đó (trạng thái quá khứ).

- Các mạch logic tổ hợp bao gồm:

+ Các mạch số học (cộng, trừ....).

+ Các bộ hợp kênh, phân kênh.

+ Các bộ mã hoá, giải mã tín hiệu.

+ Các mạch so sánh.

+ Các bộ khoá, điều khiển logic,...

2. Mạch so sánh hai số

- Mạch so sánh có nhiệm vụ so sánh hai giá trị A và B (1 bit):

+ Nếu A = B thì lối ra C = 1.

+ Nếu A \(\ne\) B thì lối ra C = 0.

- Bảng chân lí của mạch so sánh:

A | B | C | Kết luận |

0 | 0 | 1 | A = B |

0 | 1 | 0 | A ≠ B |

1 | 0 | 0 | A ≠ B |

1 | 1 | 1 | A = B |

+ Chân lí với hàng C có giá trị bằng 1, có phương trình logic:

\(C=\overline{A}\overline{B}+AB\)

+ Mạch sử dụng hai cổng NOT, hai cổng AND và một cổng OR.

- Sơ đồ logic của mạch được biểu diễn:

Câu hỏi:

@202901714113@

@202901716224@

II. MẠCH DÃY

1. Khái niệm mạch dãy

- Mạch dãy được xây dựng từ các cổng logic cơ bản.

- Lối ra của mạch:

+ Đầu ra phụ thuộc vào cả trạng thái đầu vào hiện tại và trạng thái đầu ra trước đó (trạng thái quá khứ).

- Các mạch dãy gồm:

+ Các phần tử nhớ.

+ Các Flip - Flop (Trigger).

+ Các bộ đếm.

+ Các bộ ghi dịch.

+ Các bộ chia tần.

2. Mạch đếm

a. Flip - Flop (FF hay còn gọi là trigger)

- Là phần tử nhớ có hai trạng thái ổn định tương ứng với logic 0 và 1.

- Dưới tác dụng của tín hiệu điều khiển lối vào, FF có thể:

+ Chuyển về một trong hai trạng thái cân bằng.

+ Giữ nguyên trạng thái cho đến khi có tín hiệu điều khiển tác động.

- Trạng thái tiếp theo của FF phụ thuộc vào tín hiệu lối vào và trạng thái lối ra hiện tại.

- Sử dụng Flip - Flop D gồm:

+ Lối vào dữ liệu D.

+ Lối vào xung CLK.

+ 2 lối ra Q và \(\overline{Q}\) (trạng thái ngược nhau).

- Bảng chân lí của Flip - Flop D:

CLK | D | Q | \(\overline{Q}\) | Trạng thái |

\(\downarrow\)\(\downarrow\) | x | Q | \(\overline{Q}\) | Không thay đổi |

\(\uparrow\)\(\uparrow\) | 0 | 0 | 1 | Xóa |

\(\uparrow\)\(\uparrow\) | 1 | 1 | 0 | Đặt |

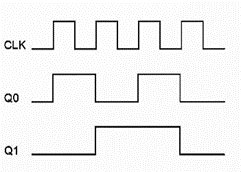

- Giản đồ thời gian của Flip - Flop D:

b. Mạch đếm nhị phân hai bit sử dụng Flip - Flop D

- Mạch đếm nhị phân là thành phần quan trọng của hệ thống số, dùng để:

+ Đếm số xung.

+ Chia tần số tạo xung thời gian làm các xung đồng hồ dùng trong:

- Máy tính.

- Thiết bị thông tin.

- Mạch đếm nhị phân nối tiếp (lối ra của FF trước đưa vào lối vào của CLK của FF sau), thực hiện đếm tiến.

- Các xung đồng hồ được đưa vào:

+ Lối vào CLK của FF0 làm chuyển trạng thái của FF0.

+ Lối ra \(\overline{Q}\) của FF0 lại được đưa tới lỗi vào CLK của FF1.

=> Làm chuyển trạng thái của FF1.

- Từ sơ đồ ta có:

+ FF0 chuyển trạng thái (Q0 từ 0 lên 1 hoặc từ 1 về 0).

+ FF1 chuyển trạng thái khi Q0 từ 1 về 0.

- Bảng chân lí của bộ đếm nhị phân hai pit:

Xung vào | Q1 | Q0 | Giá trị thập phân |

Xung xóa | 0 | 0 | 0 |

Xung 1 | 0 | 1 | 1 |

Xung 2 | 1 | 0 | 2 |

Xung 3 | 1 | 1 | 3 |

- Mạch thực hiện đếm từ 0 đến 3, khi xung thứ 4 tác dụng, mạch trở lại trạng thái ban đầu, tiếp tục một chu trình mới.

Câu hỏi:

@202901717330@

@202901719677@

@202901718314@

Bạn có thể đăng câu hỏi về bài học này ở đây